Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Description

The Adesto® AT45DB161E is a 2.3 V or 2.5 V minimum, serial-interface sequential access Flash memory ideally suited for a wide variety of digital voice, image, program code, and data storage applications. The AT45DB161E also supports the RapidS serial interface for applications requiring very high speed operation. Its 17,301,504 bits of memory are organized as 4,096 pages of 512 bytes or 528 bytes each. In addition to the main memory, the AT45DB161E also contains two SRAM buffers of 512/528 bytes each. The buffers allow receiving of data while a page in the main memory is being reprogrammed. Interleaving between both buffers can dramatically increase a system's ability to write a continuous data stream. Also, the SRAM buffers can be used as additional system scratch pad memory, and E2PROM emulation (bit or byte alterability) can be easily handled with a self-contained three step read-modify-write operation. Unlike conventional Flash memories that are accessed randomly with multiple address lines and a parallel interface, the Adesto DataFlash® uses a serial interface to sequentially access its data. The simple sequential access dramatically reduces active pin count, facilitates simplified hardware layout, increases system reliability, minimizes switching noise, and reduces package size. The device is optimized for use in many commercial and industrial applications where high-density, low-pin count, low-voltage, and low-power are essential. To allow for simple in-system re-programmability, the AT45DB161E does not require high input voltages for programming. The device operates from a single 2.3 V to 3.6 V or 2.5 V to 3.6 V power supply for the erase and program and read operations. The AT45DB161E is enabled through the Chip Select pin (CS) and accessed via a three-wire interface consisting of the Serial Input (SI), Serial Output (SO), and the Serial Clock (SCK). All programming and erase cycles are self-timed.

2. Features

1. Single 2.3 V - 3.6 V or 2.5 V - 3.6 V supply

2. Serial Peripheral Interface (SPI) compatible

- Supports SPI modes 0 and 3

- Supports RapidS™ operation

3. Continuous read capability through entire array

- Up to 85 MHz

- Low-power read option up to 15 MHz

- Clock-to-output time (tV) of 6 ns maximum

4. User-configurable page size

- 512 bytes per page

- 528 bytes per page (default)

- Page size can be factory pre-configured for 512 bytes

5. Two fully independent SRAM data buffers (512/528 bytes)

- Allows receiving data while reprogramming the main memory array

6. Flexible programming options

- Byte/Page Program (1 to 512/528 bytes) directly into main memory

- Buffer Write

- Buffer to Main Memory Page Program

7. Flexible erase options

- Page Erase (512/528 bytes)

- Block Erase (4 kB)

- Sector Erase (128 kB)

- Chip Erase (16 Mbits)

8. Program and Erase Suspend/Resume

9. Advanced hardware and software data protection features

- Individual sector protection

- Individual sector lockdown to make any sector permanently read-only

10. 128-byte, One-Time Programmable (OTP) Security Register

- 64 bytes factory programmed with a unique identifier

- 64 bytes user programmable

11. Hardware and software controlled reset options

12. JEDEC Standard Manufacturer and Device ID Read

13. Low-power dissipation

- 400 nA Ultra-Deep Power-Down current (typical)

- 3 μA Deep Power-Down current (typical)

- 25 μA Standby current (typical)

- 7 mA Active Read current (typical @ 15 MHz))

14. Endurance: 100,000 program/erase cycles per page minimum

15. Data retention: 20 years

16. Complies with full industrial temperature range

17. Green (Pb/Halide-free/RoHS compliant) packaging options

- 8-lead SOIC (0.150" wide and 0.208" wide)

- 8-pad Ultra-thin DFN (5 x 6 x 0.6mm)

- 11-ball Wafer Level Chip Scale Package

- Die in Wafer Form

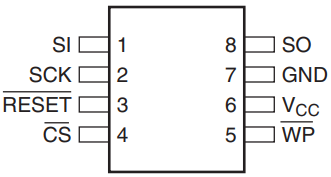

3. Pin configuration

4. AC waveform

Waveform 1 shows that the SCK signal is low when CS makes a high-to-low transition, and waveform 2 shows that the SCK signal is high when CS makes a high-to-low transition. In both cases, the output SO becomes active while the SCK signal is still low (the time SCK is low is specified as tWL). Timing waveforms 1 and 2 conform to the RapidS serial interface, but at frequencies up to 85 MHz. Waveforms 1 and 2 are compatible with SPI Mode 0 and SPI Mode 3, respectively. Waveforms 3 and 4 illustrate the general timing diagram for the RapidS serial interface. These are similar to waveforms 1 and 2, except that the output SO is not limited to becoming active during tWL. These timing waveforms are valid over the entire frequency range (maximum frequency = 85 MHz) of the RapidS serial case.

5. Using the RapidS feature

To take advantage of the RapidS feature's ability to operate at higher clock frequencies, one full clock cycle must be used to transfer data back and forth on the serial bus. DataFlash is designed to always output data on the falling edge of the SCK signal and clock data on the rising edge of SCK. For full clock cycle operation, when DataFlash outputs data on the falling edge of SCK, the host controller must wait until the next falling edge of SCK to latch the data. Likewise, the host controller must clock its data out on the rising edge of SCK to give the DataFlash a full clock cycle to latch incoming data on the next rising edge of SCK

6. System Considerations

The serial interface is controlled by serial clock (SCK), serial input (SI), and chip select (CS) pins. These The signal must rise and fall monotonically and be free of noise. Excessive noise or ringing on these pins can cause Misunderstood as multiple edges and leads to improper device operation. PCB traces must be kept to Minimum distance or proper termination to ensure proper operation. If necessary, decoupling capacitors can Added on these pins to provide filtering against noise glitches. As system complexity continues to increase, voltage regulation becomes increasingly important. any one key element The regulation scheme is its current source capability. Like all flash, the peak current is DataFlash devices occur during program and erase operations. supply voltage regulator required able to supply this peak current requirement. A lower than specified regulator may result in insufficient current. Apart from Increased system noise, insufficient current during programming or erasing can result in improper operation and Possible data corruption.