Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Description

The CAT24C208WI-GT3 is an EEPROM Serial 8−Kb I2C Dual Port internally organized as 4 segments of 256 bytes each. The CAT24C208 features a 16−byte page write buffer and can be accessed from either of two separate I2C compatible ports, DSP (SDA, SCL) and DDC (SDA, SCL). Arbitration between the two interface ports is automatic and allows the appearance of individual access to the memory from each interface.

2. Features

1. Supports Standard and Fast I2C Protocol

2. 2.5 V to 5.5 V Operation

3. 16−Byte Page Write Buffer

4. Schmitt Triggers and Noise Protection Filters on I2C Bus Input

5. Low Power CMOS Technology

6. 1,000,000 Program/Erase Cycles

7. 100 Year Data Retention

8. Industrial Temperature Range

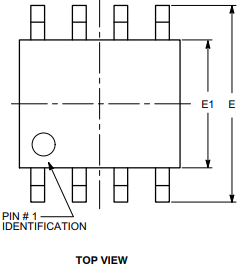

9. SOIC 8−lead Package

10. This Device is Pb−Free, Halogen Free/BFR Free, and RoHS Compliant

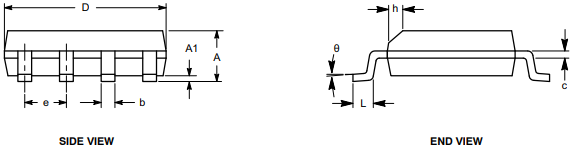

3. PIN CONFIGURATION

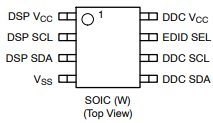

4. PIN DESCRIPTION

5. Function Description

The total storage space of CAT24C208 is 1K bytes Can be accessed from any of the two I2C interface ports, (DSP_SDA and DSP_SCL) or (DDC_SDA and DDC_SCL), and use the segment pointer at the address 60 hours. After power-up and any instructions, this section The pointer will be in the 00h segment and 00h segment of the DSP The bank selected by the DDC configuration register. The entire memory is represented as a continuous memory space From the display interface (DSP_SDA and DSP_SCL), A complete description of the DSP interface. The configuration register at address 62/63h is used Configure the operation and memory mapping of the device as From the DDC interface, (DDC_SDA and DDC_SCL). Read and write operations can be in any From showing the location in the storage space of the DSP Regardless of the state of the EDID SEL pin or Activity on the DDC interface. From the DDC interface, The memory space is displayed as two 512-byte memory banks, There are 2 00h and 01h segments on the upper and lower sides Bank. Each group of memory can be used to store E-EDID data structure. However, only one library can be read DDC port once. Active memory bank (ie The group that appears at the DDC port address A0h is Through the configuration register in 62/63h and EDID_SEL pin. Cannot write from the DDC interface Unless the DDC write enable bit is set in the device (WE = 1) Configuration register at device address 62h. The device automatically arbitrates between the two Interface to allow the appearance of personal access The memory of each interface. In a typical E-EDID application, the EDID_SEL pin is Usually connected to the "analog cable detection" pin Comply with VESA M1 standard, dual mode (analog and digital) exhibit. In this way, E-EDID appears in the address A0h on the DDC port will be analog or digital E-EDID, depending on the status of the "analog cable" Detect" pin (pin C3 of M1-DA connector).

6. Package overview