Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. describe

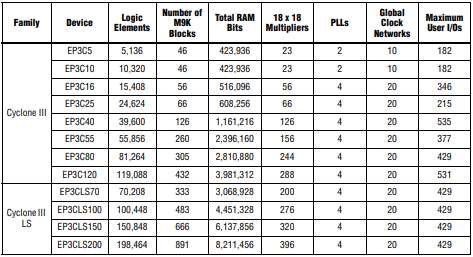

The Cyclone® III device family provides a unique combination of high functionality, low power consumption and low cost. The Cyclone III device family is based on TSMC's (TSMC) low-power (LP) process technology, silicon optimization and software functions to minimize power consumption and provide an ideal solution for your high-volume, low-power, and cost-sensitive products Scenario application. To meet unique design requirements, the Cyclone III device family provides the following two variants:

1. Cyclone III—lowest power consumption, high performance and lowest cost

2. Cyclone III LS-the lowest power FPGA with security

The density of the Cyclone III device family ranges from approximately 5,000 to 200,000 logic elements (LE) and 0.5 megabits (Mb) to 8 Mb of memory, with static power consumption of less than 1/4 watt, making it easier for you to meet your power budget . Cyclone III LS devices are the first to implement a set of silicon, software, and intellectual property (IP) level security features on low-power and high-function FPGA platforms. This set of security features protects IP tampering, reverse engineering and cloning. In addition, Cyclone III LS devices support design separation, enabling you to introduce redundancy in a single chip to reduce the size, weight, and power consumption of the application.

2. Lowest Power FPGAs

1. Lowest power consumption with TSMC low-power process technology and Altera® power-aware design flow

2. Low-power operation offers the following benefits:

- Extended battery life for portable and handheld applications

- Reduced or eliminated cooling system costs

- Operation in thermally-challenged environments

3. Hot-socketing operation support

3. Design Security Feature

1. Configuration security using advanced encryption standard (AES) with 256-bit volatile key

2. Routing architecture optimized for design separation flow with the Quartus® II software

- Design separation flow achieves both physical and functional isolation between design partitions

3. Ability to disable external JTAG port

4. Error Detection (ED) Cycle Indicator to core

- Provides a pass or fail indicator at every ED cycle

- Provides visibility over intentional or unintentional change of configuration random access memory (CRAM) bits

5. Ability to perform zeroization to clear contents of the FPGA logic, CRAM,embedded memory, and AES key

6. Internal oscillator enables system monitor and health check capabilities

4. Increased System Integration

1. High memory-to-logic and multiplier-to-logic ratio

2. High I/O count, low-and mid-range density devices for user I/O constrained applications

- Adjustable I/O slew rates to improve signal integrity

- Supports I/O standards such as LVTTL, LVCMOS, SSTL, HSTL, PCI, PCI-X, LVPECL, bus LVDS (BLVDS), LVDS, mini-LVDS, RSDS, and PPDS

- Supports the multi-value on-chip termination (OCT) calibration feature to eliminate variations over process, voltage, and temperature (PVT)

3. Four phase-locked loops (PLLs) per device provide robust clock management and synthesis for device clock management, external system clock management, and I/O interfaces

- Five outputs per PLL

- Cascadable to save I/Os, ease PCB routing, and reduce jitter

- Dynamically reconfigurable to change phase shift, frequency multiplication or division, or both, and input frequency in the system without reconfiguring the device

4. Remote system upgrade without the aid of an external controller

5. Dedicated cyclical redundancy code checker circuitry to detect single-event upset (SEU) issues

6. Nios® II embedded processor for Cyclone III device family, offering low cost and custom-fit embedded processing solutions

7. Wide collection of pre-built and verified IP cores from Altera and Altera Megafunction Partners Program (AMPP) partners

8. Supports high-speed external memory interfaces such as DDR, DDR2, SDR SDRAM, and QDRII SRAM

- Auto-calibrating PHY feature eases the timing closure process and eliminates variations with PVT for DDR, DDR2, and QDRII SRAM interfaces

5. Cyclone III Device Family Features