Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Describe

DDR SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n prefetch architecture, and its interface is designed to transmit two data words per clock cycle on the I/O pins. Single reading or The write access of DDR SDRAM actually consists of a single 2n-bit wide, one-clock-cycle data transmission of the internal DRAM core, and two corresponding n-bit-wide, one-half-clock-cycle data transmissions on the I/O pins. Two-way data strobe (DQS) is transmitted externally together with data for Data capture at the receiving end. DQS is the strobe signal for DDR SDRAM transmission READ and WRITE are executed by the memory controller. DQS aligns to the edge of the data Read and align center with the written data. x16 products have two data strobes, One for the low byte and one for the high byte. DDR SDRAM uses differential clocks (CK and CK#) to run; CK crossover Going high and CK# going low will be referred to as the rising edge of CK. Commands (address and control signals) are registered at each rising edge of CK. The input data is registered on the two edges of DQS, and the output data is referenced to the two edges The edge of DQS, and the two edges of CK. Read and write access to DDR SDRAM is burst-oriented; access starts at The selected position and the number of programs that continue to be programmed in the position order. The visit starts by registering the ACTIVE command, and then you can Followed by READ or WRITE commands. Registered address bit and The ACTIVE command is used to select the library and row to be accessed. address The bit registered at the same time as the READ or WRITE command is used to select the memory bank And the starting column position of burst access. DDR SDRAM provides programmable READ or WRITE burst length of 2, 4 or 8 Place. The automatic pre-charging function can be enabled to provide self-timed operation The precharge that starts at the end of the burst access. Like standard SDR SDRAM, the pipeline and multi-group architecture of DDR SDRAM Allows concurrent operations to provide high effective bandwidth through hiding Line precharge and activation time. Provide automatic refresh mode and power-saving power-down mode. all The input is compatible with the JEDEC standard of SSTL_2. All full drive options output It is SSTL_2, Type II compatible.

2. Features

1. VDD = 2.5V ±0.2V; VDDQ = 2.5V ±0.2V

– VDD = 2.6V ±0.1V; VDDQ = 2.6V ±0.1V (DDR400)1

2. Bidirectional data strobe (DQS) transmitted/received with data, that is, source-synchronous data capture (x16 has two – one per byte)

3. Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

4. Differential clock inputs (CK and CK#)

5. Commands entered on each positive CK edge

6. DQS edge-aligned with data for READs; centeraligned with data for WRITEs

7. DLL to align DQ and DQS transitions with CK

8. Four internal banks for concurrent operation

9. Data mask (DM) for masking write data (x16 has two – one per byte)

10. Programmable burst lengths (BL): 2, 4, or 8

11. Auto refresh

– 64ms, 8192-cycle

12. Longer-lead TSOP for improved reliability (OCPL)

13. 2.5V I/O (SSTL_2-compatible)

14. Concurrent auto precharge option supported

15. tRAS lockout supported (tRAP = tRCD)

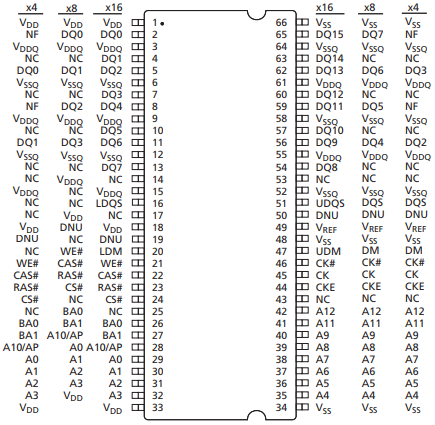

3. Pin configuration