Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Description

MT48LC32M16A2TG-75:IT:CTR is a high-speed CMOS, dynamic random access memory, containing 536,870,912 bits. It is internally configured as four groups of DRAM with synchronous interfaces. Each of the 134,217,728-bit banks of x4 is organized as 8192 rows x 4096 columns x 4 Bit. Each of the 134,217,728-bit x8 banks is organized into 8192 rows x 2048 columns by 8 bits. Each of the 134,217,728-bit x16 banks is organized into 8192 rows x 1024 columns x 16 bits. Read and write access to SDRAM is burst-oriented; access starts from the selected Position and continue at the position of the programmed number in the programming sequence. The access starts with the registration of the ACTIVE command, followed by the READ or WRITE command. Registered address bit and The ACTIVE command is used to select the bank and row to be accessed (BA[1:0] select Bank; A[12:0] select line). The registered address bit is the same as READ or The WRITE command is used to select the starting column position of burst access. SDRAM provides programmable read or write burst length (BL) of 1, 2, 4 or 8 Position or full page, with burst termination option. Automatic pre-charging function Can be enabled to provide self-timed line pre-charging, which starts at the end Burst sequence. 512Mb SDRAM uses an internal pipeline architecture to achieve high-speed operation. This architecture is compatible with the 2n rule of the prefetch architecture, but it It also allows the column address to be changed every clock cycle to achieve high-speed, completely random access. Pre-charge another bank while visiting another bank The three banks will hide the PRECHARGE cycle and provide seamless, high-speed, random access operations. The 512Mb SDRAM is designed to run in a 3.3V storage system. Auto Refresh Provide modes, as well as power-saving and power-down modes. All inputs and outputs are compatible with LVTTL. SDRAM provides substantial improvements in DRAM operating performance, including Ability to synchronize burst data at high data rates through automatic column addresses Generation, the ability to stagger between internal banks to hide the pre-charge time, and The ability to randomly change the column address every clock cycle during the burst Right to use.

2. Features

1. PC100- and PC133-compliant

2. Fully synchronous; all signals registered on positive edge of system clock

3. Internal, pipelined operation; column address can be changed every clock cycle

4. Internal banks for hiding row access/precharge

5. Programmable burst lengths: 1, 2, 4, 8, or full page

6. Auto precharge, includes concurrent auto precharge and auto refresh modes

7. Self refresh mode

8. Auto refresh

– 64ms, 8192-cycle refresh (commercial and industrial)

9. LVTTL-compatible inputs and outputs

10. Single 3.3V ±0.3V power supply

3. Options Marking

1. Configurations

– 128 Meg x 4 (32 Meg x 4 x 4 banks) 128M4

– 64 Meg x 8 (16 Meg x 8 x 4 banks) 64M8

– 32 Meg x 16 (8 Meg x 16 x 4 banks) 32M16

2. Write recovery (tWR)

– tWR = 2 CLK1 A2

3. Plastic package – OCPL2

– 54-pin TSOP II (400 mil) (standard) TG

– 54-pin TSOP II (400 mil) Pb-free P

4. Timing – cycle time

– 7.5ns @ CL = 3 (PC133) -75

– 7.5ns @ CL = 2 (PC133) -7E3

5. Self refresh

– Standard None

– Low power

6. Operating temperature range

– Commercial (0˚C to +70˚C) None

– Industrial (–40˚C to +85˚C) IT

7. Revision

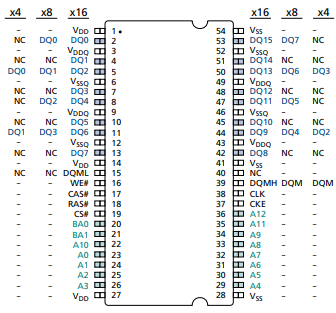

4. Pin assignment

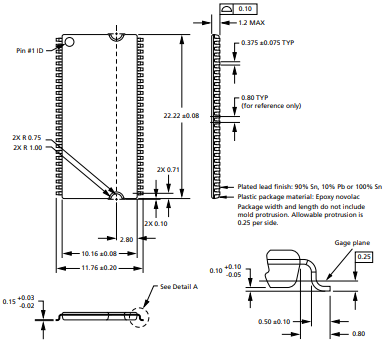

5. Package Dimensions