Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Describe

SN65HVD10, SN75HVD10, SN65HVD11,SN75HVD11, SN65HVD12DR and SN75HVD12 buses The transceiver incorporates a three-state differential line driver And differential input line receiver Single 3.3V power supply. They are designed for Balance the transmission line and meet or exceed ANSI standards TIA/EIA-485-A and ISO 8482:1993. These differential bus transceivers are monolithic Integrated circuit designed for bidirectional data Communication on a multipoint bus transmission line. The driver and receiver have high-level active and Active low level is enabled separately, you can Externally connected together as direction control. Very low device standby power supply current can This can be achieved by disabling the driver and receiver. Driver differential output and receiver differential The input is connected internally to form a differential input/Output (I/O) bus port designed to provide As long as the driver is Disable or VCC = 0. These parts have wide positive And negative common mode voltage range They are suitable for party line applications.

2. Feature

1. Working with 3.3V power supply

2. Bus pin ESD protection exceeds 16-kV HBM

3. 1/8 unit load option is available (up to 256 nodes on the bus)

4. Optional drive output conversion time 1 Mbps, 10 Mbps and 32 Mbps

5. Meets or exceeds ANSI requirements TIA/EIA-485-A

6. Bus pin short circuit protection from –7 V to 12 volts

7. Low current standby mode: 1 µA, typical

8. Open circuit, idle bus and short circuit bus fail safe Recipient

9. Thermal shutdown protection

10. Glitch-free power-on and power-off protection For hot-swappable applications

11. SN75176 package

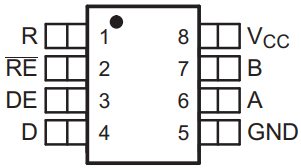

3. Pin configuration

4. Application

1. Digital motor control

2. Utility meters

3. Chassis to chassis interconnection

4. Electronic security station

5. Industrial process control

6. Building automation

7. Point of Sale (POS) terminal and network

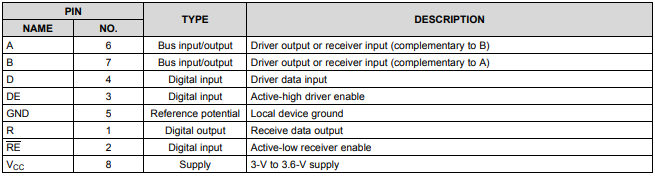

5. Pin description

6. Function description

Internal ESD protection circuit protects transceiver bus terminals from ±16-kV human body model (HBM) Electrostatic discharge and ±4-kV electrical fast transient (EFT), in accordance with IEC61000-4-4. The SN65HVD1x half-duplex series provides an internal bias of the receiver input threshold for an open circuit, Bus idle or short-circuit fault protection conditions, and 35 mV typical receiver hysteresis.

7. Device function mode

When the driver enable pin DE is logic high, the differential output A and B follow the logic state at the data input D. The logic high at D causes A to go high and B to go low. In this case, the differential output voltage is defined as VOD = VA-VB is positive. When D is low, the output state is reversed, B becomes high, A becomes low, VOD is Negative. When DE is low, both outputs become high impedance. In this case, the logic state at D does not matter. DE pin There is an internal pull-down resistor to ground; therefore, when left open, the driver is disabled (high impedance) default. The D pin has an internal pull-up resistor to VCC; therefore, when the driver is enabled, it remains open and outputs A B becomes higher and B becomes lower. When the receiver enable pin RE is logic low, the receiver is enabled. When the differential input voltage Defined as VID = VA – VB is positive and higher than the positive input threshold VIT+, receiver output R, Becomes high. When VID is negative and lower than the negative input threshold, VIT–, Receiver output, R, turn low. If VID is between VIT+ and VIT– , The output is uncertain. When RE is logic high or kept open, the receiver output is high impedance and the amplitude and polarity of VID It doesn't matter. When the transceiver is working, the internal bias of the receiver input will cause the output to become fail-safe high Disconnected from the bus (open circuit), the bus line is short-circuited (short-circuit), or the bus is not actively driven (Free bus).