Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Description

The CAV25128VE-GT3 is a EEPROM Serial 128−Kb SPI Automotive Grade 1 device internally organized as 16Kx8 bits. This features a 64−byte page write buffer and supports the Serial Peripheral Interface (SPI) protocol. The device is enabled through a Chip Select (CS) input. In addition, the required bus signals are clock input (SCK), data input (SI) and data output (SO) lines. The HOLD input may be used to pause any serial communication with the CAV25128 device. The device features software and hardware write protection, including partial as well as full array protection. On−Chip ECC (Error Correction Code) makes the device suitable for high reliability applications.

2. Features

1. Automotive AEC−Q100 Grade 1 (−40°C to +125°C) Qualified

2. 10 MHz SPI Compatible

3. 2.5 V to 5.5 V Supply Voltage Range

4. SPI Modes (0,0) & (1,1)

5. 64−byte Page Write Buffer

6. Additional Identification Page with Permanent Write Protection

7. Self−timed Write Cycle

8. Hardware and Software Protection

9. Block Write Protection

− Protect 1/4, 1/2 or Entire EEPROM Array

10. Low Power CMOS Technology

11. 1,000,000 Program/Erase Cycles

12. 100 Year Data Retention

13. 8−Lead SOIC and TSSOP Packages

14. This Device is Pb−Free, Halogen Free/BFR Free, and RoHS Compliant

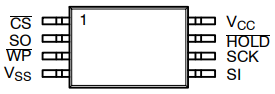

3. PIN CONFIGURATION

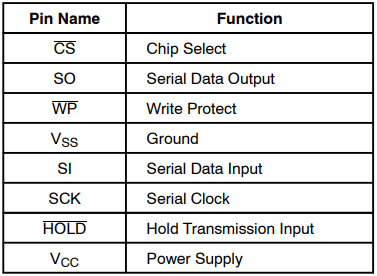

4. Pin Description

5. Function Description

CAV25128 device supports serial peripherals Interface (SPI) bus protocol, modes (0,0) and (1,1). This The device contains an 8-bit instruction register. instruction Table 7 lists the settings and related operation codes. Reading the data stored in CAV25128 is through Just provide the READ command and address. Write CAV25128, and WRITE Command, address and data, also need to be enabled A device that writes by first setting certain bits in the state Register, I will explain later. After the CS input pin changes from high to low, CAV25128 will accept any of the six commands The opcode will ignore all other possible 8-bit combinations. CAV25128 has an additional identification page that can be used for reading and writing Operation when the IPL bit in the status register is set To "1". Users can also choose to identify The page is permanently write-protected.