Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Description

GAL16V8D-25LP has a maximum propagation delay time of 3.5 ns, combined with high-performance CMOS process and electrically erasable (E2) floating gate technology, to provide the highest speed Performance available on the PLD market. High-speed erasing times (<100ms) Allows the device to be reprogrammed quickly and efficiently. The common architecture provides maximum design flexibility by Allows to configure the output logic macro cell (OLMC) in the following ways user. An important subset of the many architecture configurations possible for GAL16V8 is the listed PAL architecture In the table in the macrocell description section. GAL16V8 device Able to fully simulate any of these PAL architectures Function/fuse mapping/parameter compatibility. Unique test circuit and reprogrammable unit allow complete communication, Functional testing in DC and manufacturing processes. As a result, the grid Semiconductor provides 100% field programmability and functionality of all GAL products. In addition, 100 erase/write cycles and The required data is kept for more than 20 years.

2. Feature

1. HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— 3.5 ns Maximum Propagation Delay

— Fmax = 250 MHz

— 3.0 ns Maximum from Clock Input to Data Output

— UltraMOS® Advanced CMOS Technology

2. 50% to 75% REDUCTION IN POWER FROM BIPOLAR

— 75mA Typ Icc on Low Power Device

— 45mA Typ Icc on Quarter Power Device

3. ACTIVE PULL-UPS ON ALL PINS

4. E2CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

5. EIGHT OUTPUT LOGIC MACROCELLS

— Maximum Flexibility for Complex Logic Designs

— Programmable Output Polarity

— Also Emulates 20-pin PAL® Devices with Full Function/Fuse Map/Parametric Compatibility

6. PRELOAD AND POWER-ON RESET OF ALL REGISTERS

— 100% Functional Testability

7. APPLICATIONS INCLUDE:

— DMA Control

— State Machine Control

— High Speed Graphics Processing

— Standard Logic Speed Upgrade

8. ELECTRONIC SIGNATURE FOR IDENTIFICATION

9. LEAD-FREE PACKAGE OPTIONS

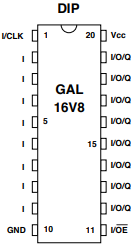

3. Pin configuration