Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Features

1. 5-stage pipeline

2. 32-bit address and data paths

3. MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

4. MIPS16e® code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8-bit and 16-bit data types

5. Simple Fixed Mapping Translation (FMT) mechanism

6. Simple dual bus interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

7. Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (rs) sign extension-dependent)

8. Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

9. EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

- PC tracing with trace compression

2. Operating Conditions

- 2.3V to 3.6V, -40ºC to +105ºC, DC to 80 MHz

3. Core: 80 MHz/105 DMIPS MIPS32® M4K®

1. MIPS16e® mode for up to 40% smaller code size

2. Code-efficient (C and Assembly) architecture

3. Single-cycle (MAC) 32x16 and two-cycle 32x32 multiply

4. Clock Management

1. 0.9% internal oscillator (on some variants)

2. Programmable PLLs and oscillator clock sources

3. Fail-Safe Clock Monitor (FSCM)

4. Independent Watchdog Timer

5. Fast wake-up and start-up

5. Power Management

1. Low-power management modes (Sleep and Idle)

2. Integrated Power-on Reset, Brown-out Reset

3. 0.5 mA/MHz dynamic current (typical)

4. 41 µA IPD current (typical)

6. Graphics Features

1. External graphics interface with up to 34 Parallel Master Port (PMP) pins:

- Interface to external graphics controller

- Capable of driving LCD directly with DMA and internal or external memory

7. Analog Features

1. ADC Module:

- 10-bit 1 Msps rate with one Sample and Hold (S&H)

- 16 analog inputs

- Can operate during Sleep mode

2. Flexible and independent ADC trigger sources

3. Comparators:

- Two dual-input Comparator modules

- Programmable references with 32 voltage points

8. Timers/Output Compare/Input Capture

1. Five General Purpose Timers:

- Five 16-bit and up to two 32-bit Timers/Counters

2. Five Output Compare (OC) modules

3. Five Input Capture (IC) modules

4. Real-Time Clock and Calendar (RTCC) module

9. Communication Interfaces

1. USB 2.0-compliant Full-Speed OTG controller

2. 10/100 Mbps Ethernet MAC with MII and RMII interface

3. CAN module:

- 2.0B Active with DeviceNet™ addressing support

4. Six UART modules (20 Mbps):

- Supports LIN 2.1 protocols and IrDA® support

5. Up to four 4-wire SPI modules (25 Mbps)

6. Up to five I2C modules (up to 1 Mbaud) with SMBus support

7. Parallel Master Port (PMP)

10. Direct Memory Access (DMA)

1. Up to eight channels of hardware DMA with automatic data size detection

2. 32-bit Programmable Cyclic Redundancy Check (CRC)

3. Six additional channels dedicated to USB, Ethernet and CAN modules

11. Input/Output

1. 15 mA or 10 mA source/sink for standard VOH/VOL and up to 22 mA for non-standard VOH1

2. 5V-tolerant pins

3. Selectable open drain and pull-ups

4. External interrupts

12. Qualification and Class B Support

1. AEC-Q100 REVH (Grade 2 -40ºC to +105ºC)

2. Class B Safety Library, IEC 60730

13. Debugger Development Support

1. In-circuit and in-application programming

2. 4-wire MIPS® Enhanced JTAG interface

3. Unlimited program and six complex data breakpoints

4. IEEE 1149.2-compatible (JTAG) boundary scan

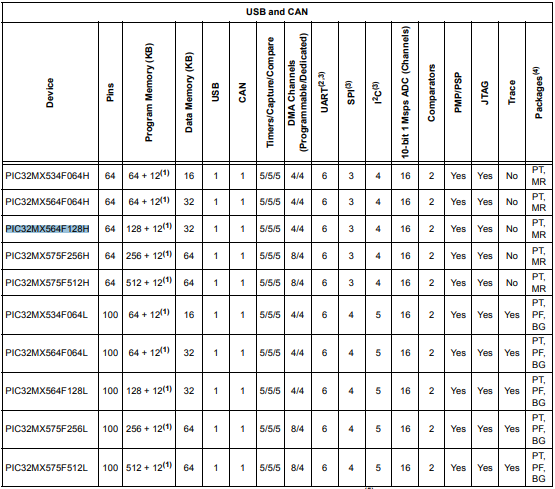

14. USB AND CAN FEATURES

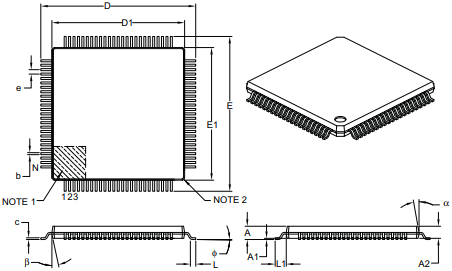

15. Package overview