Can ship immediately

Description

The microcontroller S912XEQ512J3VAG is a further development of the S12XD series, including New features to enhance system integrity and enhanced functions. These new features include Memory Protection Unit (MPU) and Error Correcting Code (ECC) on the flash memory, and Enhanced EEPROM function (EEE), enhanced XGATE, internal filter frequency Modulation phase locked loop (IPLL) and enhanced ATD. E series expands S12X products

The 208-pin version of the flagship product has a maximum capacity of 1MB flash memory and has enhanced I/O functions MC9S12XE100.

S912XEQ512J3VAG provides 32-bit performance and all the advantages and efficiency of 16-bit MCU retains the current advantages of low cost, power consumption, EMC and code size efficiency.

Users of Freescale’s existing 16-bit MC9S12 and S12X MCU series like it. High level Compatibility between S12XE and S12XD series.

An enhanced version of the S912XEQ512J3VAG series of XGATE coprocessors with enhanced performance It can be programmed in "C" language and runs at twice the frequency of the S12X bus, and has The instruction set is optimized for data movement, logic and bit manipulation instructions and can be used All peripheral modules on the device. New enhanced version improves interrupt handling It has complete functions and is fully compatible with existing XGATE modules.

The S912XEQ512J3VAG series includes standard on-chip peripherals, including up to 64Kb of RAM, Eight asynchronous serial communication interfaces (SCI), three serial peripheral device interfaces (SPI), one 8 Channel IC/OC Enhanced Capture Timer (ECT), two 16 channels, 12-bit analog-to-digital converter, one 8 Channel pulse width modulator (PWM), five CAN 2.0 A, B software compatible modules (MSCAN12), Two inter-IC bus blocks (IIC), an 8-channel 24-bit periodic interrupt timer (PIT) and an 8-channel 16-bit Standard timer module (TIM).

The S912XEQ512J3VAG series uses 16-bit wide access, and all peripheral devices and memories have no wait state.

The 144/208-Pin version provides a non-multiplexed expansion bus interface, which can be easily implemented Interface with external memory.

In addition to the I/O ports available in each module, up to 26 I/O ports with interrupts are provided.

The function to allow wake-up from STOP or WAIT mode.

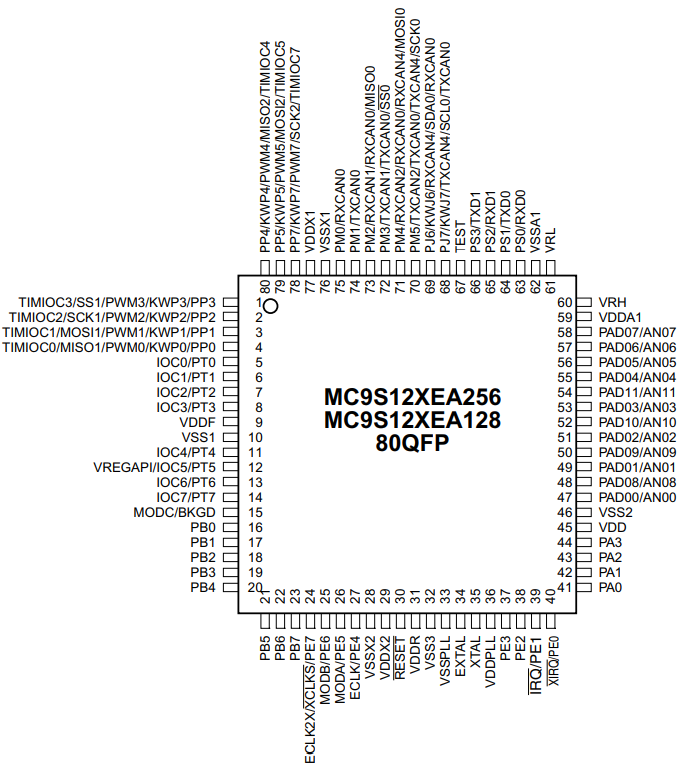

Pin MAPBGA, 144-pin LQFP, 112-pin LQFP or 80-pin QFP options.

Features

Features of the S912XEQ512J3VAG Family are listed here. for the peripheral features that are available on the different family members.

1. 16-Bit CPU12X

2. INT (interrupt module)

3. EBI (external bus interface)(available in 208-Pin and 144-Pin packages only)

4. MMC (module mapping control)

5. DBG (debug module)

6. BDM (background debug mode)

7. MPU (memory protection unit)

8. XGATE

9. OSC_LCP (oscillator)

10. IPLL (Internally filtered, frequency modulated phase-locked-loop clock generation)

11. CRG (clock and reset generation)

12. Memory Options

13. Flash General Features

14. D-Flash Features

15. Emulated EEPROM Features

16. Two 16-channel, 12-bit Analog-to-Digital Converters

17. Five MSCAN (1 M bit per second, CAN 2.0 A, B software compatible modules)

18. ECT (enhanced capture timer)

19. TIM (standard timer module)

20. PIT (periodic interrupt timer)

21. 8 PWM (pulse-width modulator) channels

22. Three Serial Peripheral Interface Modules (SPI)

23. Eight Serial Communication Interfaces (SCI)

24. Two Inter-IC bus (IIC) Modules

25. On-Chip Voltage Regulator

26. Low-power wake-up timer (API)

27. Input/Output

28. Package Options

29. 50MHz maximum CPU bus frequency, 100MHz maximum XGATE bus frequency