Can ship immediately

Due to market price fluctuations,if you need to purchase or consult the price.You can contact us or emial to us: brenda@hongda-ic.com

1. Describe

The S9S12G128AMLHR family is a line of automotive 16-bit microcontrollers optimized for Low cost, high performance and low pin count. This family is designed to bridge high-end 8-bit Microcontrollers and high-performance 16-bit microcontrollers such as the MC9S12XS family. This MC9S12G family targets general automotive applications requiring CAN or LIN/J2602 communication. Typical examples of these applications include body controllers, occupant detection, door Modules, Seat Controllers, RKE Receivers, Smart Actuators, Lighting Modules and Smart Junction Boxes. The MC9S12G-Family uses many of the same features found on the MC9S12XS- and MC9S12P-Family, Includes error correcting code (ECC) on flash memory, fast analog-to-digital converter (ADC) and Frequency Modulated Phase Locked Loop (IPLL) for improved EMC performance. The MC9S12G family is optimized for smaller program memory down to 16k. To simplify Customers use it with a 4-byte erasable sector size EEPROM. The MC9S12G family offers all the advantages and efficiencies of a 16-bit MCU while maintaining low Cost, power, EMC and code size efficiency benefits currently enjoyed by NXP users Existing 8-bit and 16-bit MCU families. Like the MC9S12XS-Family, the MC9S12G-Family runs 16-bit No need to wait for extensive access to all peripherals and memory. The MC9S12G series is available in 100-pin LQFP, 64-pin LQFP, 48-pin LQFP/QFN, 32-pin LQFP, and 20-pin TSSOP package options and Designed to maximize feature count, especially for lower pin count packages. also I/O ports available in each module, more I/O ports are interrupt capable, allowing Wake from stop or wait mode.

2. Features

1. S12 CPU core

2. Up to 240 Kbyte on-chip flash with ECC

3. Up to 4 Kbyte EEPROM with ECC

4. Up to 11 Kbyte on-chip SRAM

5. Phase locked loop (IPLL) frequency multiplier with internal filter

6. 4–16 MHz amplitude controlled Pierce oscillator

7. 1 MHz internal RC oscillator

8. Timer module (TIM) supporting up to eight channels that provide a range of 16-bit input capture, output compare, counter, and pulse accumulator functions

9. Pulse width modulation (PWM) module with up to eight x 8-bit channels

10. Up to 16-channel, 10 or 12-bit resolution successive approximation analog-to-digital converter (ADC)

11. Up to two 8-bit digital-to-analog converters (DAC)

12. Up to one 5V analog comparator (ACMP)

13. Up to three serial peripheral interface (SPI) modules

14. Up to three serial communication interface (SCI) modules supporting LIN communications

15. Up to one multi-scalable controller area network (MSCAN) module (supporting CAN protocol 2.0A/B)

17. On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

18. Autonomous periodic interrupt (API)

19. Precision fixed voltage reference for ADC conversions

20. Optional reference voltage attenuator module to increase ADC accuracy

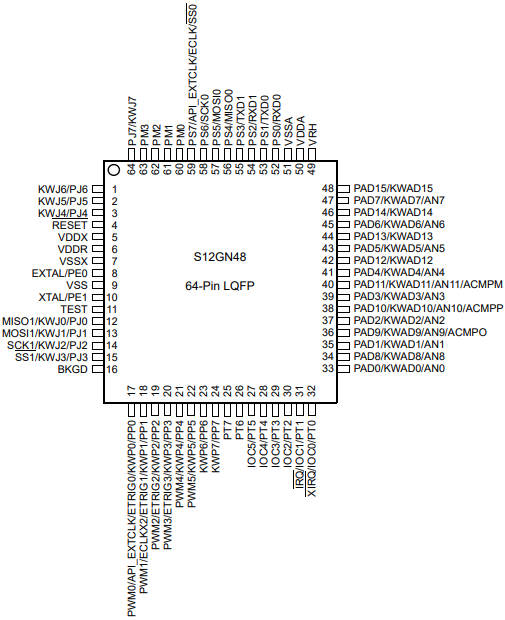

3. Pin configuration

4. Central Processor Unit (CPU)

1. Full 16-bit data paths supports efficient arithmetic operation and high-speed math execution

2. Includes many single-byte instructions. This allows much more efficient use of ROM space.

3. Extensive set of indexed addressing capabilities, including:

- Using the stack pointer as an indexing register in all indexed operations

- Using the program counter as an indexing register in all but auto increment/decrement mode

- Accumulator offsets using A, B, or D accumulators

- Automatic index predecrement, preincrement, postdecrement, and postincrement (by –8 to +8)

5. Port Integration Module (PIM)

1. Data registers and data direction registers for ports A, B, C, D, E, T, S, M, P, J and AD when used as general-purpose I/O

2. Control registers to enable/disable pull devices and select pullups/pulldowns on ports T, S, M, P, J and AD on per-pin basis

3. Single control register to enable/disable pull devices on ports A, B, C, D and E, on per-port basis and on BKGD pin

4. Control registers to enable/disable open-drain (wired-or) mode on ports S and M

5. Interrupt flag register for pin interrupts on ports P, J and AD

6. Control register to configure IRQ pin operation

7. Routing register to support programmable signal redirection in 20 TSSOP only

8. Routing register to support programmable signal redirection in 100 LQFP package only

9. Package code register preset by factory related to package in use, writable once after reset. Also includes bit to reprogram routing of API_EXTCLK in all packages.

10. Control register for free-running clock outputs

6. Main External Oscillator (XOSCLCP)

1. Loop control Pierce oscillator using a 4 MHz to 16 MHz crystal

- Current gain control on amplitude output

- Signal with low harmonic distortion

- Low power

- Good noise immunity

- Eliminates need for external current limiting resistor

- Transconductance sized for optimum start-up margin for typical crystals

- Oscillator pins can be shared w/ GPIO functionality